DARPA מתכננת מהפיכה במתודולוגיית תכנון ASIC

31 אוגוסט, 2015

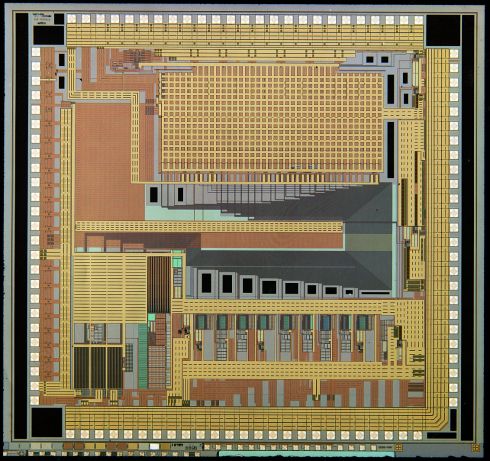

סוכנות DARPA משיקה תוכנית חדשה שנועדה להוזיל משמעותית ולקצר לעשירית את זמני הפיתוח של רכיבים ייעודיים (ASIC) ליישומים צבאיים

DARPA משיקה תוכנית חדשה שנועדה להוזיל משמעותית ולקצר לעשירית את זמני הפיתוח של רכיבים ייעודיים ליישומים צבאיים

הזמן הרב הדרוש לתכנן שבב חדש, העלות הגבוהה ותהליכי האימות הממושכים, הפכו למטרד המציק לתעשיית השבבים בעולם כולו, ומתבטא בירידה מתמשכת בפיתוח שבבי ASIC חדשים. כעת מתברר שגם משרד הביטחון האמריקאי מוטרד מהמגמה המתמשכת הזו.

בשבוע שעבר פירסמה הסוכנות למחקרי ביטחון מתקדמים במשרד ההגנה האמריקאי (DARPA) בקשה לקבלת הצעות עבור תוכנית חדשה אשר תגדיר מחדש את כל תהליכי התיכנון והפיתוח של רכיבים ייעודיים למערכות ביטחוניות. מטרת התוכנית היא לשנות באופן דרמטי את אופן התכנון, זמני התכנון ועלויות התכנון של רכיבים חדשים, כדי לאפשר שימוש ברכיבים ייעודיים (ASIC) במערכות צבאיות מתקדמות.

התוכנית החדשה קיבלה את הכינוי CRAFT, שזה קיצור של Circuit Realization At Faster Timescales , ותקציב של 30 מיליון דולר לשלוש שנים. ההצעות יתקבלו עד ה-5 לאוקטובר, והתוכנית תתחיל לפעול בחודש אפריל 2016.

הפתרונות הגנריים לא מתאימים

בעמוד הבית של פרוייקט CRAFT, הסוכנות מסבירה שבפועל הצורך ברכיבים צבאיים ייעודיים נמצא בעלייה עקב העלייה בדרישות ממערכות האלקטרוניקה הצבאיות. מערכות המתאמות את הפעילות של כלים בלתי מאויישים, המרה בזמן אמת של אותות מכ"ם לתמונות תלת-מימדיות, או נגישות מיידית למידע ברזולוציה גבוהה המגיע מחיישנים בשדה הקרב, דורשים רכיבים יעילים וייעודיים בעלי ביצועים גבוהים מאוד.

אלא שבפועל, מתודולוגיות התכנון של רכיבים חדשים גורמות לכך שהמערכות הצבאיות נאלצות להתפשר על רכיבים בעלי צריכה אנרגיה גבוהה מאוד, שאינה מתאימה לדרישות האמיתיות.

אלא שבפועל, מתודולוגיות התכנון של רכיבים חדשים גורמות לכך שהמערכות הצבאיות נאלצות להתפשר על רכיבים בעלי צריכה אנרגיה גבוהה מאוד, שאינה מתאימה לדרישות האמיתיות.

"זה לא שהמהנדסים אינם מסוגלים לפתח את הרכיבים הדרושים, אלא שכיום הפיתוח של רכיב ייעודי נמשך לפחות שנתיים בהשקעה של עד 100 מיליון דולר לרכיב. התוצאה: התעשייה עושה שימוש ברכיבים גנריים מוכנים מהמדף אשר מתאימים לשימושים כלליים, וסומכת על התוכנה כדי שהרכיבים יבצעו את הפעולות הנדרשות מהם.

"הדבר מקצר מאוד את זמני הפיתוח והיישום, אולם כרוך באספקת מוצרים אלקטרוניים זוללי אנרגיה המריצים מעגלים מיותרים". מנהל תוכנית CRAFT במחלקת Microsystems שלDARPA , לינטון סלמון, הסביר שמטרת התוכנית היא לפתח מתודולוגיית תכנון שבבים מהירה, המאפשרת לייצר אותם במתקני ייצור שונים, באופן שניתן יהיה לבצע שימוש חוזר בפתרונות שהוכחו כמוצלחים.

המבחן של מכ"ם Gotcha

סלמון: "חיל האוויר מפתח כיום מכ"ם Gotcha שיאפשר לזהות כלי-טיס על רקע סביבה אורבנית ולהפיק תמונות תלת מימדיות ברזולוציה גבוהה של הסביבה האורבנית. כיום המכ"ם הזה זקוק למחשב-על קרקעי כדי לבצע את כל החישובים ולהמיר את האותות מהמכ"ם למידע טקטי יעיל. אלא שהתלות בקו תקשורת אל תחנת קרקע פוגע בביצועים המבצעיים של המערכת. התוכנית תסייע בהבאת עוצמת המיחשוב אל המל"ט או אל מטוס הקרב עצמו".

ספציפית, המטרה היא לאפשר שימוש בתהליכי ייצור מסחריים בגיאומטריות של 16 ננומטר ו-14 ננומטר המשמשות היום לייצור רכיבים סדרתיים. "רכיב המיועד לעבד תמונות ממכ"ם מוטס לא צריך להריץ גיליון אלקטרוני או מעבד תמלילים. מדוע להעלות לפלטפורמה הצבאית אולר שווייצרי שלם, כאשר אנחנו זקוקים למברג בלבד"?

מטרת התוכנית היא לקצר לעשירית את זמני התכנון של רכיבי ASIC חדשים, למספר חודשים במקום מספר שנים. פיתוח מסגרת המאפשרת להעביר את התכנון בקלות לתהליך ייצור חדש כאשר הוא יוצא לתעשייה, ולאפשר לשמר תיעוד וקניין רוחני באופן שניתן יהיה להשתמש בו בעתיד בדורות חדשים של המערכות הצבאיות.

200 מיליון טרנזיסטורים ב-30 שבועות

במסמכי התוכנית שנבדקו על-ידי Techtime, מובאת דוגמא מעשית למצב הנוכחי וליעדי התוכנית. סוכנות DARPA בדקה את המאפיינים הממוצעים של פיתוח רכיב ASIC צבאי המיוצר בגיאומטריה של 28 ננומטר. מהבדיקה עולה שתכנון הרכיב נעשה על-ידי צוות של 10 מהנדסים, הוא כולל 100 מיליון טרנזיסטורים וכל התהליך נמשך 130 שבועות.

המטרה היא שצוות דומה ישלים את כל התהליך ב-30 שבועות ויתכנן רכיב הכולל 200 מיליון טרנזיסטורים. היעד יושג באמצעות סילוק צווארי בקבוק. כך למשל, כיום תהליך ההבאה לייצור תופס כ-40% מהזמן. DARPA רוצה לקצר את התהליך. השאר מוקדש לתכנון, אולם 60% מזמן התכנון מוקדש לאימות התכנון – וגם זה שלב ש-DARPA רוצה לקצר דרמטית.

החברות שיגשו לתוכנית, ייאלצו לעמוד בתנאים מעשיים מוגדרים. כך למשל, אחד מהתנאים של חברות שישתתפו בתוכנית היא להגיע בסיום השלב הראשון (15 חודשים) למצב שבו הן מצליחות לקצר פי 10 את זמן התכנון של רכיב SoC לפי בחירתן, הכולל לפחות 200 אלף שערים לוגיים וכולל מספר בלוקים לאותות מעורבים, מספר בלוקים של זיכרון SRAM ושימוש ב-IP ממקור חיצוני.

פורסם בקטגוריות: חדשות , סמיקונדקטורס

פורסם בתגיות: featured